Copy Link

Add to Bookmark

Report

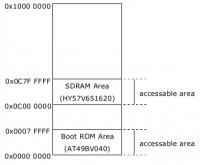

Nintendo 64 Memory Map

Nintendo 64 Toolkit: opcodes v1.1 by anarko <anarko@flashback.net>

Part H: Nintendo 64 memory map released on 1999-04-21

----------------------------------------------------------------------------

*************************************************************************

** Overview **

*************************************************************************

0x0000 0000 to 0x03EF FFFF RDRAM Memory

0x03F0 0000 to 0x03FF FFFF RDRAM Registers

0x0400 0000 to 0x040F FFFF SP Registers

0x0410 0000 to 0x041F FFFF DP Command Registers

0x0420 0000 to 0x042F FFFF DP Span Registers

0x0430 0000 to 0x043F FFFF MIPS Interface (MI) Registers

0x0440 0000 to 0x044F FFFF Video Interface (VI) Registers

0x0450 0000 to 0x045F FFFF Audio Interface (AI) Registers

0x0460 0000 to 0x046F FFFF Peripheral Interface (PI) Registers

0x0470 0000 to 0x047F FFFF RDRAM Interface (RI) Registers

0x0480 0000 to 0x048F FFFF Serial Interface (SI) Registers

0x0490 0000 to 0x04FF FFFF Unused

0x0500 0000 to 0x05FF FFFF Cartridge Domain 2 Address 1

0x0600 0000 to 0x07FF FFFF Cartridge Domain 1 Address 1

0x0800 0000 to 0x0FFF FFFF Cartridge Domain 2 Address 2

0x1000 0000 to 0x1FBF FFFF Cartridge Domain 1 Address 2

0x1FC0 0000 to 0x1FC0 07BF PIF Boot ROM

0x1FC0 07C0 to 0x1FC0 07FF PIF RAM

0x1FC0 0800 to 0x1FCF FFFF Reserved

0x1FD0 0000 to 0x7FFF FFFF Cartridge Domain 1 Address 3

0x8000 0000 to 0xFFFF FFFF External SysAD Device

*************************************************************************

** Detailed **

*************************************************************************

0x0000 0000 to 0x03EF FFFF RDRAM memory:

-----------------------------------------

0x0000 0000 to 0x001F FFFF RDRAM range 0

0x0020 0000 to 0x003F FFFF RDRAM range 1

0x0040 0000 to 0x03EF FFFF Unused

0x03F0 0000 to 0x03FF FFFF RDRAM registers:

--------------------------------------------

RDRAM_BASE_REG - 0x03F00000

0x03F0 0000 to 0x03F0 0003 RDRAM_CONFIG_REG or

RDRAM_DEVICE_TYPE_REG

0x03F0 0004 to 0x03F0 0007 RDRAM_DEVICE_ID_REG

0x03F0 0008 to 0x03F0 000B RDRAM_DELAY_REG

0x03F0 000C to 0x03F0 000F RDRAM_MODE_REG

0x03F0 0010 to 0x03F0 0013 RDRAM_REF_INTERVAL_REG

0x03F0 0014 to 0x03F0 0017 RDRAM_REF_ROW_REG

0x03F0 0018 to 0x03F0 001B RDRAM_RAS_INTERVAL_REG

0x03F0 001C to 0x03F0 001F RDRAM_MIN_INTERVAL_REG

0x03F0 0020 to 0x03F0 0023 RDRAM_ADDR_SELECT_REG

0x03F0 0024 to 0x03F0 0027 RDRAM_DEVICE_MANUF_REG

0x03F0 0028 to 0x03FF FFFF Unknown

0x0400 0000 to 0x0400 FFFF SP registers:

-----------------------------------------

SP_BASE_REG - 0x04040000

0x0400 0000 to 0x0400 0FFF SP_DMEM read /write

0x0400 1000 to 0x0400 1FFF SP_IMEM read /write

0x0400 2000 to 0x0403 FFFF Unused

0x0404 0000 to 0x0404 0003 SP_MEM_ADDR_REG

Master, SP memory address

(RW): [11:0] DMEM /IMEM address

[12] 0=DMEM,1=IMEM

0x0404 0004 to 0x0404 0007 SP_DRAM_ADDR_REG

Slave, SP DRAM DMA address

(RW): [23:0] RDRAM address

0x0404 0008 to 0x0404 000B SP_RD_LEN_REG

SP read DMA length

(RW): [11:0] length

[19:12] count

[31:20] skip

direction: I /DMEM <- RDRAM

0x0404 000C to 0x0404 000F SP_WR_LEN_REG

SP write DMA length

(RW): [11:0] length

[19:12] count

[31:20] skip

direction: I /DMEM to RDRAM

0x0404 0010 to 0x0404 0013 SP_STATUS_REG

SP status

(W): [0] clear halt (R): [0] halt

[1] set halt [1] broke

[2] clear broke [2] dma busy

[3] clear intr [3] dma full

[4] set intr [4] io full

[5] clear sstep [5] single step

[6] set sstep [6] interrupt on break

[7] clear intr on break [7] signal 0 set

[8] set intr on break [8] signal 1 set

[9] clear signal 0 [9] signal 2 set

[10] set signal 0 [10] signal 3 set

[11] clear signal 1 [11] signal 4 set

[12] set signal 1 [12] signal 5 set

[13] clear signal 2 [13] signal 6 set

[14] set signal 2 [14] signal 7 set

[15] clear signal 3

[16] set signal 3

[17] clear signal 4

[18] set signal 4

[19] clear signal 5

[20] set signal 5

[21] clear signal 6

[22] set signal 6

[23] clear signal 7

[24] set signal 7

0x0404 0014 to 0x0404 0017 SP_DMA_FULL_REG

SP DMA full

(R): [0] valid bit

dma full

0x0404 0018 to 0x0404 001B SP_DMA_BUSY_REG

SP DMA busy

(R): [0] valid bit

dma busy

0x0404 001C to 0x0404 001F SP_SEMAPHORE_REG

SP semaphore

(R): [0] semaphore flag (set on read)

(W): [] clear semaphore flag

0x0404 0020 to 0x0407 FFFF Unused

0x0408 0000 to 0x0408 0003 SP_PC_REG

SP PC

(RW): [11:0] program counter

0x0408 0004 to 0x0408 0007 SP_IBIST_REG

SP IMEM BIST REG

(W): [0] BIST check (R): [0] BIST check

[1] BIST go [1] BIST go

[2] BIST clear [2] BIST done

[6:3] BIST fail

0x0408 0008 to 0x040F FFFF Unused

0x0410 0000 to 0x041F FFFF DP command registers:

-------------------------------------------------

DPC_BASE_REG - 0x04100000

0x0410 0000 to 0x0410 0003 DPC_START_REG

DP CMD DMA start

(RW): [23:0] DMEM /RDRAM start address

0x0410 0004 to 0x0410 0007 DPC_END_REG

DP CMD DMA end

(RW): [23:0] DMEM /RDRAM end address

0x0410 0008 to 0x0410 000B DPC_CURRENT_REG

DP CMD DMA end

(R): [23:0] DMEM /RDRAM current address

0x0410 000C to 0x0410 000F DPC_STATUS_REG

DP CMD status

(W): [0] clear xbus_dmem_dma (R): [0] xbus_dmem_dma

[1] set xbus_dmem_dma [1] freeze

[2] clear freeze [2] flush

[3] set freeze [3] start gclk

[4] clear flush [4] tmem busy

[5] set flush [5] pipe busy

[6] clear tmem ctr [6] cmd busy

[7] clear pipe ctr [7] cbuf ready

[8] clear cmd ctr [8] dma busy

[9] clear clock ctr [9] end valid

[10] start valid

0x0410 0010 to 0x0410 0013 DPC_CLOCK_REG

DP clock counter

(R): [23:0] clock counter

0x0410 0014 to 0x0410 0017 DPC_BUFBUSY_REG

DP buffer busy counter

(R): [23:0] clock counter

0x0410 0018 to 0x0410 001B DPC_PIPEBUSY_REG

DP pipe busy counter

(R): [23:0] clock counter

0x0410 001C to 0x0410 001F DPC_TMEM_REG

DP TMEM load counter

(R): [23:0] clock counter

0x0410 0020 to 0x041F FFFF Unused

0x0420 0000 to 0x042F FFFF DP span registers:

----------------------------------------------

DPS_BASE_REG - 0x04200000

0x0420 0000 to 0x0420 0003 DPS_TBIST_REG

DP tmem bist

(W): [0] BIST check (R): [0] BIST check

[1] BIST go [1] BIST go

[2] BIST clear [2] BIST done

[10:3] BIST fail

0x0420 0004 to 0x0420 0007 DPS_TEST_MODE_REG

DP span test mode

(RW): [0] Span buffer test access enable

0x0420 0008 to 0x0420 000B DPS_BUFTEST_ADDR_REG

DP span buffer test address

(RW): [6:0] bits

0x0420 000C to 0x0420 000F DPS_BUFTEST_DATA_REG

DP span buffer test data

(RW): [31:0] span buffer data

0x0420 0010 to 0x042F FFFF Unused

0x0430 0000 to 0x043F FFFF MIPS interface (MI) registers:

----------------------------------------------------------

MI_BASE_REG - 0x04300000

0x0430 0000 to 0x0430 0003 MI_INIT_MODE_REG or MI_MODE_REG

MI init mode

(W): [6:0] init length (R): [6:0] init length

[7] clear init mode [7] init mode

[8] set init mode [8] ebus test mode

[9 /10] clr /set ebus test mode [9] RDRAM reg mode

[11] clear DP interrupt

[12] clear RDRAM reg

[13] set RDRAM reg mode

0x0430 0004 to 0x0430 0007 MI_VERSION_REG or MI_NOOP_REG

MI version

(R): [7:0] io

[15:8] rac

[23:16] rdp

[31:24] rsp

0x0430 0008 to 0x0430 000B MI_INTR_REG

MI interrupt

(R): [0] SP intr

[1] SI intr

[2] AI intr

[3] VI intr

[4] PI intr

[5] DP intr

0x0430 000C to 0x0430 000F MI_INTR_MASK_REG

MI interrupt mask

(W): [0 /1] clear /set SP mask (R): [0] SP intr mask

[2 /3] clear /set SI mask [1] SI intr mask

[4 /5] clear /set AI mask [2] AI intr mask

[6 /7] clear /set VI mask [3] VI intr mask

[8 /9] clear /set PI mask [4] PI intr mask

[10 /11] clear /set DP mask [5] DP intr mask

0x0430 0010 to 0x043F FFFF Unused

0x0440 0000 to 0x044F FFFF Video interface (VI) registers:

-----------------------------------------------------------

VI_BASE_REG - 0x04400000

0x0440 0000 to 0x0440 0003 VI_STATUS_REG or VI_CONTROL_REG

VI status /control

(RW): [1:0] type[1:0] (pixel size)

0: blank (no data, no sync)

1: reserved

2: 5 /5 /5 /3 ("16" bit)

3: 8 /8 /8 /8 (32 bit)

[2] gamma_dither_enable (normally on, unless "special effect")

[3] gamma_enable (normally on, unless MPEG /JPEG)

[4] divot_enable (normally on if antialiased,

unless decal lines)

[5] reserved - always off

[6] serrate (always on if interlaced, off if not)

[7] reserved - diagnostics only

[9:8] anti-alias (aa) mode[1:0]

0: aa & resamp (always fetch extra lines)

1: aa & resamp (fetch extra lines if needed)

2: resamp only (treat as all fully covered)

3: neither (replicate pixels, no interpolate)

[11] reserved - diagnostics only

[15:12] reserved

0x0440 0004 to 0x0440 0007 VI_ORIGIN_REG or VI_DRAM_ADDR_REG

VI origin

(RW): [23:0] frame buffer origin in bytes

0x0440 0008 to 0x0440 000B VI_WIDTH_REG or VI_H_WIDTH_REG

VI width

(RW): [11:0] frame buffer line width in pixels

0x0440 000C to 0x0440 000F VI_INTR_REG or VI_V_INTR_REG

VI vertical intr

(RW): [9:0] interrupt when current half-line = V_INTR

0x0440 0010 to 0x0440 0013 VI_CURRENT_REG or VI_V_CURRENT_LINE_REG

VI current vertical line

(RW): [9:0] current half line, sampled once per line (the lsb of

V_CURRENT is constant within a field, and in

interlaced modes gives the field number - which is

constant for non-interlaced modes)

- Writes clears interrupt line

0x0440 0014 to 0x0440 0017 VI_BURST_REG or VI_TIMING_REG

VI video timing

(RW): [7:0] horizontal sync width in pixels

[15:8] color burst width in pixels

[19:16] vertical sync width in half lines

[29:20] start of color burst in pixels from h-sync

0x0440 0018 to 0x0440 001B VI_V_SYNC_REG

VI vertical sync

(RW): [9:0] number of half-lines per field

0x0440 001C to 0x0440 001F VI_H_SYNC_REG

VI horizontal sync

(RW): [11:0] total duration of a line in 1 /4 pixel

[20:16] a 5-bit leap pattern used for PAL only (h_sync_period)

0x0440 0020 to 0x0440 0023 VI_LEAP_REG or VI_H_SYNC_LEAP_REG

VI horizontal sync leap

(RW): [11:0] identical to h_sync_period

[27:16] identical to h_sync_period

0x0440 0024 to 0x0440 0027 VI_H_START_REG or VI_H_VIDEO_REG

VI horizontal video

(RW): [9:0] end of active video in screen pixels

[25:16] start of active video in screen pixels

0x0440 0028 to 0x0440 002B VI_V_START_REG or VI_V_VIDEO_REG

VI vertical video

(RW): [9:0] end of active video in screen half-lines

[25:16] start of active video in screen half-lines

0x0440 002C to 0x0440 002F VI_V_BURST_REG

VI vertical burst

(RW): [9:0] end of color burst enable in half-lines

[25:16] start of color burst enable in half-lines

0x0440 0030 to 0x0440 0033 VI_X_SCALE_REG

VI x-scale

(RW): [11:0] 1 /horizontal scale up factor (2.10 format)

[27:16] horizontal subpixel offset (2.10 format)

0x0440 0034 to 0x0440 0037 VI_Y_SCALE_REG

VI y-scale

(RW): [11:0] 1 /vertical scale up factor (2.10 format)

[27:16] vertical subpixel offset (2.10 format)

0x0440 0038 to 0x044F FFFF Unused

0x0450 0000 to 0x045F FFFF Audio interface (AI) registers:

-----------------------------------------------------------

AI_BASE_REG - 0x04500000

0x0450 0000 to 0x0450 0003 AI_DRAM_ADDR_REG

AI DRAM address

(W): [23:0] starting RDRAM address (8B-aligned)

0x0450 0004 to 0x0450 0007 AI_LEN_REG

AI length

(RW): [14:0] transfer length (v1.0) - Bottom 3 bits are ignored

[17:0] transfer length (v2.0) - Bottom 3 bits are ignored

0x0450 0008 to 0x0450 000B AI_CONTROL_REG

AI control

(W): [0] DMA enable - if LSB == 1, DMA is enabled

0x0450 000C to 0x0450 000F AI_STATUS_REG

AI status

(R): [31] /[0] ai_full (addr & len buffer full)

[30] ai_busy

Note that a 1to0 transition in ai_full will set interrupt

(W): clear audio interrupt

0x0450 0010 to 0x0450 0013 AI_DACRATE_REG

AI DAC sample period register

(W): [13:0] dac rate

- vid_clock /(dperiod + 1) is the DAC sample rate

- (dperiod + 1) >= 66 * (aclockhp + 1) must be true

0x0450 0014 to 0x0450 0017 AI_BITRATE_REG

AI bit rate

(W): [3:0] bit rate (abus clock half period register - aclockhp)

- vid_clock /(2*(aclockhp + 1)) is the DAC clock rate

- The abus clock stops if aclockhp is zero

0x0450 0018 to 0x045F FFFF Unused

0x0460 0000 to 0x046F FFFF Peripheral interface (PI) registers:

----------------------------------------------------------------

PI_BASE_REG - 0x04600000

0x0460 0000 to 0x0460 0003 PI_DRAM_ADDR_REG

PI DRAM address

(RW): [23:0] starting RDRAM address

0x0460 0004 to 0x0460 0007 PI_CART_ADDR_REG

PI pbus (cartridge) address

(RW): [31:0] starting AD16 address

0x0460 0008 to 0x0460 000B PI_RD_LEN_REG

PI read length

(RW): [23:0] read data length

0x0460 000C to 0x0460 000F PI_WR_LEN_REG

PI write length

(RW): [23:0] write data length

0x0460 0010 to 0x0460 0013 PI_STATUS_REG

PI status

(R): [0] DMA busy (W): [0] reset controller

[1] IO busy (and abort current op)

[2] error [1] clear intr

0x0460 0014 to 0x0460 0017 PI_BSD_DOM1_LAT_REG or PI_DOMAIN1_REG

PI dom1 latency

(RW): [7:0] domain 1 device latency

0x0460 0018 to 0x0460 001B PI_BSD_DOM1_PWD_REG

PI dom1 pulse width

(RW): [7:0] domain 1 device R /W strobe pulse width

0x0460 001C to 0x0460 001F PI_BSD_DOM1_PGS_REG

PI dom1 page size

(RW): [3:0] domain 1 device page size

0x0460 0020 to 0x0460 0023 PI_BSD_DOM1_RLS_REG

PI dom1 release

(RW): [1:0] domain 1 device R /W release duration

0x0460 0024 to 0x0460 0027 PI_BSD_DOM2_LAT_REG or PI_DOMAIN2_REG

PI dom2 latency

(RW): [7:0] domain 2 device latency

0x0460 0028 to 0x0460 002B PI_BSD_DOM2_PWD_REG

PI dom2 pulse width

(RW): [7:0] domain 2 device R /W strobe pulse width

0x0460 002C to 0x0460 002F PI_BSD_DOM2_PGS_REG

PI dom2 page size

(RW): [3:0] domain 2 device page size

0x0460 0030 to 0x0460 0033 PI_BSD_DOM2_RLS_REG

PI dom2 release

(RW): [1:0] domain 2 device R /W release duration

0x0460 0034 to 0x046F FFFF Unused

0x0470 0000 to 0x047F FFFF RDRAM interface (RI) registers:

-----------------------------------------------------------

RI_BASE_REG - 0x04700000

0x0470 0000 to 0x0470 0003 RI_MODE_REG

RI mode

(RW): [1:0] operating mode

[2] stop T active

[3] stop R active

0x0470 0004 to 0x0470 0007 RI_CONFIG_REG

RI config

(RW): [5:0] current control input

[6] current control enable

0x0470 0008 to 0x0470 000B RI_CURRENT_LOAD_REG

RI current load

(W): [] any write updates current control register

0x0470 000C to 0x0470 000F RI_SELECT_REG

RI select

(RW): [2:0] receive select

[2:0] transmit select

0x0470 0010 to 0x0470 0013 RI_REFRESH_REG or RI_COUNT_REG

RI refresh

(RW): [7:0] clean refresh delay

[15:8] dirty refresh delay

[16] refresh bank

[17] refresh enable

[18] refresh optimize

0x0470 0014 to 0x0470 0017 RI_LATENCY_REG

RI latency

(RW): [3:0] DMA latency /overlap

0x0470 0018 to 0x0470 001B RI_RERROR_REG

RI error

(R): [0] nack error

[1] ack error

0x0470 001C to 0x0470 001F RI_WERROR_REG

RI error

(W): [] any write clears all error bits

0x0470 0020 to 0x047F FFFF Unused

0x0480 0000 to 0x048F FFFF Serial interface (SI) registers:

------------------------------------------------------------

SI_BASE_REG - 0x04800000

0x0480 0000 to 0x0480 0003 SI_DRAM_ADDR_REG

SI DRAM address

(R /W): [23:0] starting RDRAM address

0x0480 0004 to 0x0480 0007 SI_PIF_ADDR_RD64B_REG

SI address read 64B

(W): [] any write causes a 64B DMA write

0x0480 0008 to 0x0480 000B Reserved

0x0480 000C to 0x0480 000F Reserved

0x0480 0010 to 0x0480 0013 SI_PIF_ADDR_WR64B_REG

SI address write 64B

(W): [] any write causes a 64B DMA read

0x0480 0014 to 0x0480 0017 Reserved

0x0480 0018 to 0x0480 001B SI_STATUS_REG

SI status

(W): [] any write clears interrupt

(R): [0] DMA busy

[1] IO read busy

[2] reserved

[3] DMA error

[12] interrupt

0x0480 001C to 0x048F FFFF Unused

Unused:

-------

0x0490 0000 to 0x04FF FFFF Unused

Cartridge Domain 2(Address 1):

------------------------------

0x0500 0000 to 0x05FF FFFF Cartridge Domain 2

0x0500 0508 - some roms read from this address.

SRAM could be here

Cartridge Domain 1(Address 1):

------------------------------

0x0600 0000 to 0x07FF FFFF Cartridge Domain 1

This address seems to be where

the n64ddrive would be addressed

0x0800 0000 to 0x0FFF FFFF Cartridge Domain 2

SRAM could be here

Cartridge Domain 1(Address 2):

------------------------------

0x1000 0000 to 0x1000 003F ROM header:

---------------------------------------

0x1000 0000 initial PI_BSB_DOM1_LAT_REG value

0x1000 0001 initial PI_BSB_DOM1_PGS_REG value

0x1000 0002 initial PI_BSB_DOM1_PWD_REG value

0x1000 0003 initial PI_BSB_DOM1_PGS_REG value

0x1000 0004 to 0x1000 0007 Clock Rate

0x1000 0008 to 0x1000 000B Boot address offset

0x1000 000C to 0x1000 000F Release offset

0x1000 0010 to 0x1000 0013 CRC1

0x1000 0014 to 0x1000 0017 CRC2

0x1000 0018 to 0x1000 001F Unused

0x1000 0020 to 0x1000 0033 Image name

0x1000 0034 to 0x1000 003A Unused

0x1000 003B Manufacturer ID

0x1000 003C to 0x1000 003D Cartridge ID

0x1000 003E Country code

0x1000 003F Unused

0x1000 0040 to 0x1000 0B6F RAMROM_BOOTSTRAP_OFFSET

0x1000 0B70 to 0x1000 0FEF RAMROM_FONTDATA_OFFSET

0x1000 0FF0 to 0x1000 0FFF Unused

0x1000 1000 to 0x10FF 9FFF RAMROM_GAME_OFFSET

0x10FF A000 to 0x10FF AFFF RAMROM_APP_READ_ADDR

0x10FF B000 to 0x10FF BFFF RAMROM_APP_WRITE_ADDR

0x10FF C000 to 0x10FF CFFF RAMROM_RMON_READ_ADDR

0x10FF D000 to 0x10FF DFFF RAMROM_RMON_WRITE_ADDR

0x10FF E000 to 0x10FF EFFF RAMROM_PRINTF_ADDR

0x10FF F000 to 0x10FF FFFF RAMROM_LOG_ADDR

0x1100 0000 to 0x17FF FFFF Unused

0x1800 0000 to 0x1800 0003 GIO Interrupt Register (R)

0x1800 0004 to 0x1800 03FF Unused

0x1800 0400 to 0x1800 0403 GIO Sync Register (R /W)

0x1800 0404 to 0x1800 07FF Unused

0x1800 0800 to 0x1800 0803 Cartridge interrupt Register (R)

0x1800 0804 to 0x1F39 FFFF Unused

PIF Boot ROM:

-------------

0x1FC0 0000 PIF_ROM_START

0x1FC0 07BF PIF_ROM_END

PIF (JoyChannel) RAM:

---------------------

0x1FC0 07C0 PIF_RAM_START

0x1FC0 07C4 (16 low bits) Status of controller:

%X X X X X X X X X X X X X X X X

A B Z ST U D L R ? ? PL PR CU CD CL CR

A,B,Z,ST = A,B,Z, Start buttons

U,D,L,R = Joypad directions

?,? = Unknown

PL,PR = Pan left, Pan right buttons

CU,CD,CL,CR = C buttons (up,down,left,right)

0x1FC0 07FF PIF_RAM_END

Reserved:

---------

0x1FC0 0800 to 0x1FCF FFFF Reserved

Cartridge Domain 1(Address 3):

------------------------------

0x1FD0 0000 to 0x7FFF FFFF Unknown

0x8000 0000 to 0xffff ffff external SysAD device

-------------------------------------------------

0x8000 0000 to 0x9FFF FFFF kseg0 (Mirror of 0x0000 0000 to 0x1FFF FFFF)

0xA000 0000 to 0xBFFF FFFF kseg1 (Mirror of 0x0000 0000 to 0x1FFF FFFF)

0xC000 0000 to 0xDFFF FFFF ksseg (TLB mapped)

0xE000 0000 to 0xFFFF FFFF kseg3 (TLB mapped)